1. Introduction

Saving electrical energy is considered one of the most important components in domestic and industrial developments. It is needed directly or indirectly in almost all industrial sectors. The increase in the electrical energy demand and consumption leads to an increase in the system fault levels. It is impractical to change the rating of the equipment and devices included in the system structure and branch circuits to accommodate the increasing fault currents. From economic prospective, the cost of equipment such as circuit breakers and transformers in power grids is very expensive. To protect the expensive equipment and devices in power systems from the increasing fault currents, Fault Current Limiters (FCLs) provide more cost-effective solutions to save the system assets.

Several devices to limit the fault current have been proposed in recent years. Among these devices, the electronically controlled fuse can be used to interrupt the fault current before the first peak. The need of replacement after every operation is a major drawback which makes them incompatible with HV systems [1]. Classical circuit breakers can limit fault current using speed of operation and magnetic effect on arcing [2]. However, classical circuit breakers with high-current interrupting capabilities are bulky and expensive electromechanical systems.

The superconducting fault current limiter (SFCL) has been shown as one of the promising options to solve the problem of the increased fault currents. SFCL typically offers fast fault current limiting capability, compact design, and high efficiency (even with including the refrigeration burden). However, SFCL is not recommended for system protection with auto-reclosure facility as it does not have a fast recovery time [3], [4].

With the development of high-power semiconductor technology, such as new thyristors with higher voltage and higher current ratings, efforts have been made to develop effective solid state circuit breakers and fault current limiters [5], [6], [7]. The Solid-State Circuit-Breaker (SSCB) offers a quick and arcless operation. There are no moving parts or contact arcing wear; hence, a larger number and higher speed of operations can be equipped. However, large energy loss and limited power rating in the current power electronic elements are the main barriers to use SSCB.

In order to avoid the aforementioned issues, this paper presents a new approach of the fault current limiter. The main objective in this approach is to develop a hybrid current limiting and interrupting device (HCLID) which can be used successfully as an ultra-fast short-circuit protection means for low voltage AC or DC industrial installations. Through this paper, we present a significantly improved and simplified approach that may replace the expensive and higher power losses of power semiconductors included in ultra-fast switching elements such as Integrated Gate-Commutated Thyristor (IGCT). Compared to SCR-based hybrid FCL types, the proposed technique that is based on self-turn-off device is superior. It is smaller in size, better in dynamic performance, and simpler in the control approach and circuitry. Topology and control strategies of the proposal HCLID are described in the next paper sections. Different system conditions are simulated in Piecewise Linear Electrical Circuit Simulation (PLECS). Simulation results show that the proposed HCLID is an appropriate means to interrupt higher short-circuit currents at zero current contact separation.

2. FCL function in low voltage ac systems

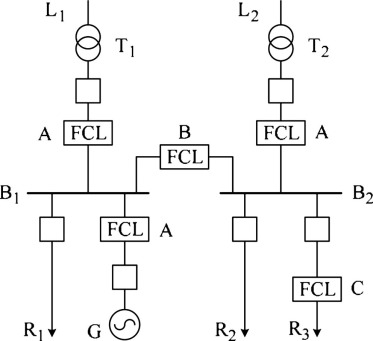

Typically, FCL is important for high voltage systems, but the constant growth of modern low voltage AC power distribution system capacity, and the parallel operation of large AC low voltage supply sources result in an increase in the level of prospective short-circuit currents. So, there arises the problem of how to limit them, in order to ensure a more reliable operation of the system equipment and the switchgear apparatus. Consequently, FCLs and interrupting devices in typical low-voltage distribution networks become among the most important features. The location and the voltage class of the FCL installation are based on the FCL targeted function. Fig. 1 shows three possible configurations that could be appropriate for FCL installation [6]. FCL installed in position ‘A’ can help in reducing fault currents and preventing transformer damages. FCL installed in the bus tie, position ‘B’, can isolate the faulty bus and maintain the pre-fault voltage level on the unfaulted bus. Through normal operation, the paralleled transformers usually provide lower impedance and better voltage regulation, so that tap-changing transformers can be avoided. Smaller and less expensive FCLs can be installed on lateral feeders, as shown in position ‘C’, to provide protection of old and/or overstressed equipment that is difficult to be replaced, such as underground cables or transformers in faults.

Figure 1. Main positions for the FCL in power grid [6].

Figure 1. Main positions for the FCL in power grid [6].3. HCLID structures and principles of operation

The HCLID configuration incorporated in a single-phase low voltage distribution network is shown in Fig. 2. It consists of a solid state commutation circuit, a saturable core reactor, a fast mechanical contact (main switch), and the energy absorbing element (ZnO). HCLID components are connected in parallel. The commutation circuit, connected to the terminals A and B, includes a single-phase half-controlled bridge-type scheme based on self-turn-off devices, such as IGCTs (IGCT1, IGCT2) and diodes (D1, D2). It includes also the branch with a pre-charged condenser CCom. and the inductance, LCom.. The current limitation facility in the presented HCLID is based on the current-limiting element of the saturable core reactor in series with the auxiliary switch. The mechanical contacts of the HCLID utilize one part of an electrodynamic repulsion drive, which is actuated by a power electronic circuit. The forced current zero can be coordinated with the instant of the auxiliary contact separation. In this device setup, an ultra-fast current interruption with no electric arc formation can be achieved.

Figure 2. The circuit layout of the improved HCLID.

Figure 2. The circuit layout of the improved HCLID.At normal operation, the main contact is closed and carries the line current, while everything else is OFF. When a fault occurs, the control circuit determines whether the short circuit current exceeds a pre-set value V1; at this moment, a control signal, released from the control circuit, triggers the electrodynamic drive to open the main contact. Once the main contact is open, the current is forced through the saturable core reactor during fault current limitation mode, and the current limitation mode is able to limit the peak and RMS fault currents for a variety of fault current levels. The control system typically compares the magnitude of the current through the saturable core reactor with a reference value V2. Once the current magnitude exceeds V2, two control signals will be triggered from the control circuit, shown in Fig. 3. The two signals will be conveyed simultaneously: one to switch the commutation circuit on and the other to initiate the auxiliary contact opening by electrodynamic drive.

Figure 3. The control scheme implemented in PLECS program.

Figure 3. The control scheme implemented in PLECS program.The control scheme is designed to easily detect the direction of the fault current. The activation of the commutation thyristors (IGCT1 or IGCT2) depends on the direction of the fault current if. Supposing that this current flows from to A to B, the IGCT1 will be switched on. The commutation current, i1, in the auxiliary contact flowing from the positive terminal of commutation capacitor, CCom., through the diode D2, will have an opposite direction to the fault current if. Hence, the current summation through the auxiliary contact becomes zero. Between the instant of the main contact separation and the triggering instant of the commutation circuit, the currents i1 and iD1 as well as the currents i2 and iD2are equal. Immediately after the instant of the triggering of the commutation circuit the currents iD1 and iD2 have profiles defined by a new rule. The diode D2now carries the fault current if that still increases, while diode D1 carries the differential current (ic − if) till the instant of the current ic equals the fault current if. At this time the diode D1 turns off and the fault current if reaches its maximum value and the recovery voltage appears across the mechanical switch, while the commutation capacitor CCom is still charging. The voltages across the switch and the capacitor CCom increase with time.

Supposing that the fault current flows from B to A terminal (refer to Fig. 2) the sequence of the events is similar to the sequence of events described above, and only IGCT2 will be triggered on instead of IGCT1.

4. Control scheme operation

The control scheme is implemented in PLECS using standard logic blocks listed in the PLECS library [8]. The control circuit of the HCLID, including short-circuit current detection system and gate signals to both the semiconductor switch and the electrodynamic drive to initiate the main and auxiliary contact, is shown in Fig. 3. The control algorithm used in detecting the fault and maintaining the faulted state is based on two key methods of detection. The first method of the controller is explained as follows. The load current is measured as iLoad and the absolute value of the measurement iLoad is first compared to zero, to check whether the fault current is in the positive or negative cycle of the current waveform. Also, this value is compared with two arbitrary preset values; if the magnitude of the current exceeds this value, then a fault has occurred and the controller operates the HCLID as previously described.

The second method of detection, measures the slope of the fault current in comparison with normal current slope to verify whether the current value is increasing. This makes sure that the current is allowed to increase till it reaches a preset maximum value. At this instant the control circuit sends the appropriate signals to both the semiconductor switch and the electrodynamic drive.

The controller has six inputs and three outputs applied to the HCLID. The six inputs are as follows: the load current iLoad, commutation capacitor current ic, fault current limitation iFCL, current through the main contact isw, V1, and V2. Each input signal is necessary to properly operate the proposed HCLID control system. V1, and V2 are predefined values. The controller outputs are the gate signals for the main contact, axillary contact signal, and the triggering signal for the commutation circuit. The controller outputs are typically logic signals that determine whether the system is experiencing a fault or not.

Once a fault condition is detected by the control algorithm, the correct order of operation is then set to separate the contacts of the main switch. Once the main switch is open, a verification of zero current through the mechanical contact is needed before turning on the auxiliary switch, as shown in Fig. 3. By waiting to triggering the commutation circuit until the current through the branch with saturable core reactor reaches to acceptable and safe value, the arc typically seen when opening up a breaker would be nonexistent thus lengthening the life of the mechanical contact switch. Also, the control strategy can detect the fault current direction and helps the fast mechanical switch to separate its contacts in a fixed time at all fault inception angles.

5. Design parameters and optimization

5.1. Selection of the switching element

The HCLID has a set of requirements that must be met by choosing a suitable switching device to make the HCLID capable of delivering the stated performance (limiting and interrupting the fault current safely). The desirable features for the solid-state switches are as follows:

-

•

High blocking voltage,

-

•

High continuous current capability,

-

•

Low on-state voltage drop,

-

•

Low conduction loss,

-

•

High switching speed and low loss, and

-

•

Suitable control technique and thermal management.

Many power semiconductor devices have been developed for the HCLID applications such as the insulated gate bipolar transistors (IGBT), SCR, gate turn-off (GTO) thyristor, emitter turn-off thyristors (ETO), and integrated gate-commutated thyristors (IGCT) [9], [10]. These devices offer some improved characteristics compared with earlier conventional silicon devices.

For high power applications, traditionally, a high power SCR is used in [9] as the symmetrical power semiconductor device for a FCL. The operation of the SCR in a solid state FCL has advantages over others in multioperation capability, lower voltage drop, lower cost and higher reliability. However, SCRs does not have the forced turn-off capability. Besides, and due to low switching frequency, the dynamic performance is low and a large filter is needed to attenuate the harmonics.

The Insulated-Gate Bipolar Transistor (IGBT) [10] has desirable qualities such as fast switching time, high reliability, and voltage controllable, and has low gate drive power consumption. However, IGBT works in a transistor mode during on-state, and has a high conduction loss comparing with the GTO type devices.

For high voltage and current applications, the GTO device has been the candidate choice for a fully controllable semiconductor switch due to its large current and off-state voltage capabilities. This device can be turned off through its gate controls at any time during the period of operation. This function is a desirable characteristic for fault current limitation and circuit breaker action. However, it has a limited switching frequency and high switching losses and requires a complex gate drive circuit [11].

With the emergence of the Integrated Gate Commutated Thyristor (IGCT) [12], the aforementioned shortcomings have been overcome. By combining the high blocking voltage ratings of the thyristor and blocking current with high reliability of the transistor, IGCT is thought to have low on-state voltage drop, low conduction loss, and fast switching times (within μs). The present high power asymmetric IGCT devices are applicable to the proposed FCLs. The available IGCT device with the maximum voltage and current ratings is made by ABB and can be chosen as IGCT1 and IGCT2 of the HCLID shown in Fig. 2. The type is 5SHY 35L4510. The main parameters of the IGCTs are listed in Table 1[13].

Table 1. The nominal ratings of the OF5SHY 35L4510 IGCT.

| Symbol | Parameters | Value |

|---|---|---|

| VDRM | Repetitive peak off-state voltage | 4500 V |

| VDC-link | Permanent DC voltage | 2800 V |

| ITGQM | Max. controllable turn-off current | 4000 A |

| IT(AV)M | Max. average on-state current | 1700 A |

| IT(RMS) | Max. RMS on-state current | 2670 A |

| di/dtmax | Max. rate of rise of on state current | 200 A/µs |

| VFO | Device blocking voltage | 1.4 V |

| rF | On-resistance | 0.032vmΩ |

The most significant parameters for selection are VDClink, ITRMS, and ITGQM. The maximum rate of rise of on state current di/dtmax is a very important parameter for the safety of IGCT devices. This is usually specified in the IGCT data sheets. IGCTs are used predominantly as snubberless devices in high-frequency PWM applications, so dv/dt do not deserve to be considered.

5.2. Operation principles of the saturable core reactor

The objective of the saturable core reactor is to find a solution to limit the prospective fault current (peak and R.M.S) to be within an acceptable value. This value is typically higher than the rated current value, but it is less than the maximum operating value of protection devices such as circuit breakers (CB) [14]. By limiting the prospective fault current within these ranges, the existing HCLID can interrupt the fault current at lower values of commutation parameters (CCom., LCom., and VCom.) without changing the coordination setting of the protective devices.

The operation of the saturable iron core FCLs is based on saturating the iron core above the Qknee of the hysteresis curve in a ferromagnetic material which is the point where the iron core inductance becomes negligible. This point corresponds to the upper right corner of the B-H curve as shown in Fig. 4. The most important advantage of HCLID with saturable core is that the core saturation effect makes the FCL inherently react to a fault.

Figure 4. The B-H hysteresis curve of a ferromagnetic material.

Figure 4. The B-H hysteresis curve of a ferromagnetic material.The hybrid system will include a new concept using a Neodymium (NdFeB) permanent magnet as the limiting impedance as well as a novel controller to control this new conceptual system. The use of a Neodymium (NdFeB) permanent magnet as the limiting impedance reduces size, cost, weight, increases reliability, and eliminates DC biasing and cooling costs. The parameters of the ferromagnetic NdFeB materials, shown in Table 2, are used as inputs for the PLECS simulation model [14].

Table 2. NdFeB material properties.

| Parameter | Symbol | Value |

|---|---|---|

| Number of winding turns | N | 60 |

| Cross-sectional area of core (m2) | Acore | 0.04129 |

| Mean path length (m) | Lmean | 1.6256 |

| Remanence flux density (T) | Brem | 1.3 |

| Saturation flux density (T) | Bsat | 1.5 |

| Coercivity (kA/m) | Hc | 994.718 |

| Saturation coercivity (kA/m) | Hsat | 1114.085 |

| Electrical resistivity (Ω m) | ρ | 1.6 * 10−6 |

| Permeability of free space (H/m) | µ0 | 4л * 10−7 |

5.3. Selection of the commutation circuit parameters (LCOM, CCOM, and VCOM)

The general idea is to interrupt the fault current at or close to zero current cross-over. In AC circuit the phenomena occur periodically twice at each cycle. A forced zero before the natural one can be done by the use of commutation principle. This method is based on the superposition of an auxiliary oscillatory current on the fault current so that an artificial current zero can be obtained. It enables the circuit breaker to interrupt the fault current before the peak of the first half cycle.

The commutation principles are described whereby the current in the main circuit is brought to zero by a commutation from a pre charged capacitor. The counter current injection from the commutation capacitor current is also used to produce a rapid extinction of arcs established between the HCLID mechanical contacts. The commutation circuit parameters could drastically influence the HCLID performance. The parameters of the commutation circuit should be selected according to the critical fault inception angle.

The aim of this section was to illustrate that HCLID design can constitute an effective limitation of fault currents in the AC mains, at fault clearance time less than a fault period of line frequency and without generation of excessive switching over voltage. The required features of the HCLID can be achieved by the proper selection of the counter current injection circuit (commutation circuit) LCom, CCom, and VCom by the use of an ultra-fast drive to open the main contact.

The optimal values of commutation circuit parameters have to satisfy the following equations:(1)(2)Here, A1 and A2 are arbitrary constants:wherewhere

LCom.: Commutation inductance,

CCom.: Commutation capacitance,

VCom.: Commutation capacitor initial voltage,

t1: Time of triggering commutation circuit,

t2: Auxiliary contact separation starts,

t4: Final fault current interruption and end of the recovery voltage,

Icm: Maximum value of the capacitance discharge current,

ωCom: Commutation frequency.

The most critical parameter that has a complex effect on the current interruption process is the value of the commutation inductance, which can be determined in (1).

The capacitance and the maximum stored energy within the commutation capacitor (described in (2)) determine mainly the cost of the HCLID. Commutation capacitance has great effect on the capacitor discharge current, the let through current, recovery voltage and maximum capacitor charge voltage. The maximum value of the capacitor discharge current, diode D1current and the let through fault current is directly proportional to the increase in initial voltage across the commutation capacitance.

6. Simulation results and discussion

In order to verify the validity of the proposed HCLID, various device simulations based on PLECS for the circuit shown in Fig. 2 are accomplished. The normal current through the system is 1000 A, as shown in Fig. 5. When the fault occurs, the prospective fault current in the system reaches 50 kA due to the fast transient and the inductive load in the system. The fault current magnitude greatly exceeds the power requirements of any devices operating in the system and justifies the urgent need for a CLID to be placed for protection.

Figure 5. Prospective fault current without HCLID in the system.

Figure 5. Prospective fault current without HCLID in the system.Fig. 6 shows the current waveforms when the saturable core reactor of the HCLID only limits the potential fault current to approximately 55% of the prospective fault current. The HCLID will interrupt the fault current after limitation process.

Figure 6. The limited fault current without the interruption process.

Figure 6. The limited fault current without the interruption process.To achieve this, simulations were undertaken of the same fault circuit parameters, commutation circuit parameters and the same initial state. The fault circuit parameters and the commutation circuit parameters used in PLECS simulation are presented in Table 3.

Table 3. HCLID simulation parameters.